systemverilog 数字系统设计,SystemVerilog数字系统设计概述

时间:2024-12-04 来源:网络 人气:

SystemVerilog数字系统设计概述

SystemVerilog是一种高级硬件描述语言(HDL),它结合了Verilog和VHDL的优点,并引入了面向对象编程(OOP)的概念。在数字系统设计中,SystemVerilog因其强大的功能和灵活性而被广泛应用。本文将介绍SystemVerilog数字系统设计的基本概念、设计流程以及一些关键技术和工具。

SystemVerilog基础语法

数据类型:SystemVerilog支持多种数据类型,包括整数、实数、枚举、字符串等。

变量和常量:变量用于存储数据,常量用于定义不变的值。

运算符:SystemVerilog支持算术、逻辑、关系和位运算符。

控制结构:包括if-else、for、while等,用于控制程序的执行流程。

模块和类:模块是SystemVerilog的基本单元,类是面向对象编程中的基本单元。

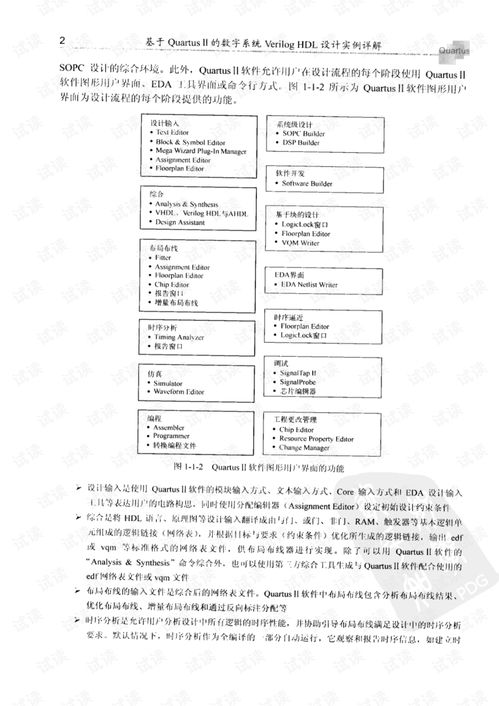

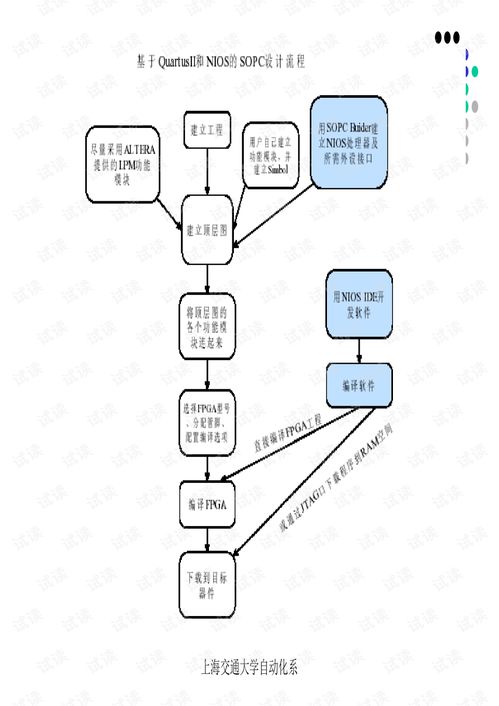

数字系统设计流程

数字系统设计通常包括以下步骤:

需求分析:明确系统的功能、性能和约束条件。

系统设计:根据需求分析,设计系统的架构和模块。

模块实现:使用SystemVerilog编写各个模块的代码。

仿真验证:使用仿真工具对设计进行测试,确保其符合预期。

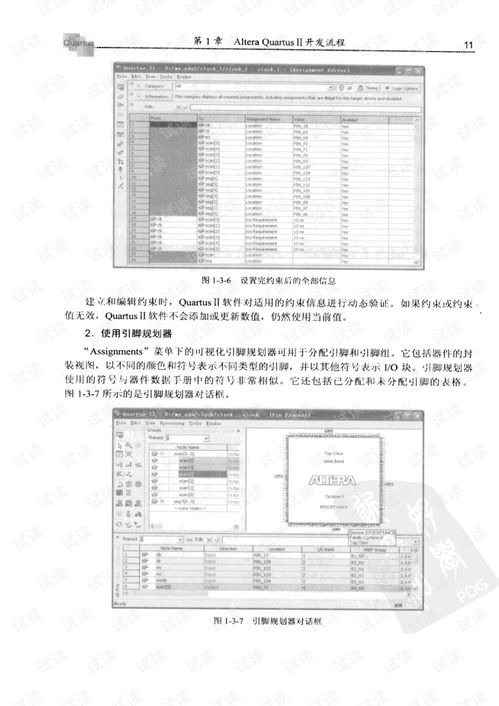

综合和布局布线:将SystemVerilog代码转换为硬件描述,并完成布局布线。

制造和测试:将设计制造为实际的硬件,并进行测试。

关键技术和工具

在SystemVerilog数字系统设计中,以下技术和工具至关重要:

UVM(Universal Verification Methodology):UVM是一种通用的验证方法,它提供了一套完整的验证框架和库,用于提高验证效率和覆盖率。

SystemVerilog-AMS(Analog-Mixed-Signal):SystemVerilog-AMS允许在SystemVerilog中描述模拟和混合信号系统,从而实现模拟和数字系统的协同设计。

SystemVerilog-AL(Algorithmic Language):SystemVerilog-AL允许使用C语言风格的语法编写算法,从而提高算法描述的效率和可读性。

综合工具:如Synopsys的Vivado、Cadence的Genus等,用于将SystemVerilog代码转换为硬件描述。

案例分析

以下是一个简单的SystemVerilog数字系统设计案例,用于实现一个4位加法器:

```systemverilog

module adder4bit(

input [3:0] a,

input [3:0] b,

output [4:0] sum

assign sum = a + b;

endmodule

在这个例子中,`adder4bit`模块接受两个4位输入`a`和`b`,并输出一个5位的和`sum`。这个简单的模块展示了SystemVerilog的基本语法和模块结构。

SystemVerilog是一种功能强大的数字系统设计工具,它结合了Verilog和VHDL的优点,并引入了面向对象编程的概念。通过掌握SystemVerilog的基础语法、设计流程和关键技术和工具,工程师可以高效地设计和验证数字系统。本文简要介绍了SystemVerilog数字系统设计的相关知识,希望对读者有所帮助。

相关推荐

教程资讯

教程资讯排行