system verilog数字系统设计,二、System Verilog简介

时间:2024-11-27 来源:网络 人气:

System Verilog数字系统设计:理论与实践结合的典范

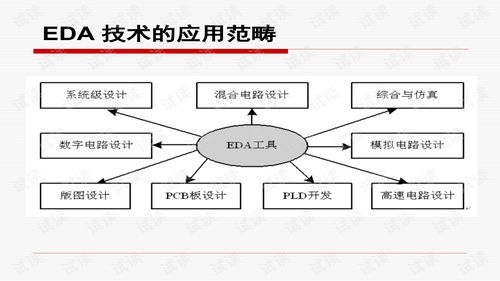

随着电子技术的飞速发展,数字系统设计在各个领域都扮演着至关重要的角色。System Verilog作为一种强大的硬件描述语言(HDL),在数字系统设计中得到了广泛应用。本文将介绍System Verilog的基本概念、设计流程以及在实际项目中的应用,旨在帮助读者更好地理解和掌握System Verilog数字系统设计。

二、System Verilog简介

System Verilog是Verilog HDL的扩展,它结合了Verilog和VHDL的优点,具有强大的行为级、结构级和系统级描述能力。System Verilog支持多种设计风格,包括行为描述、结构描述和系统级描述,这使得它在数字系统设计中具有很高的灵活性和可扩展性。

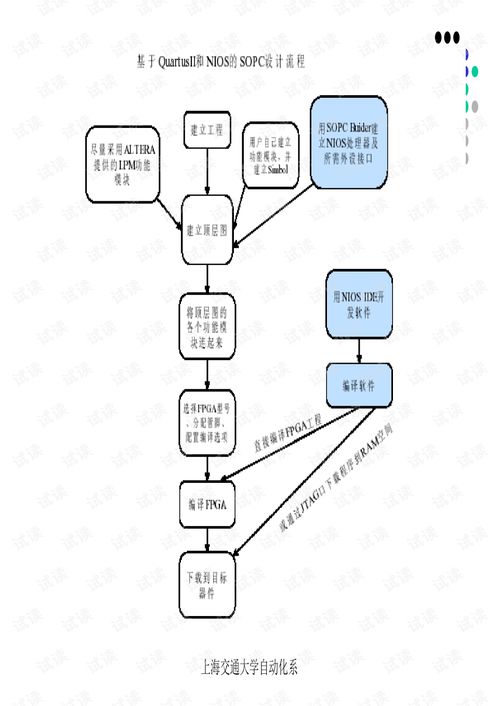

三、System Verilog设计流程

System Verilog数字系统设计流程主要包括以下步骤:

1. 需求分析

在开始设计之前,首先要明确系统的需求,包括功能、性能、功耗、面积等指标。

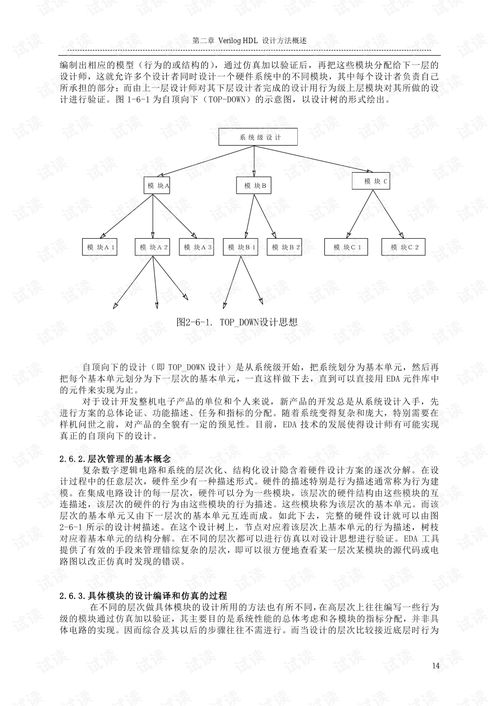

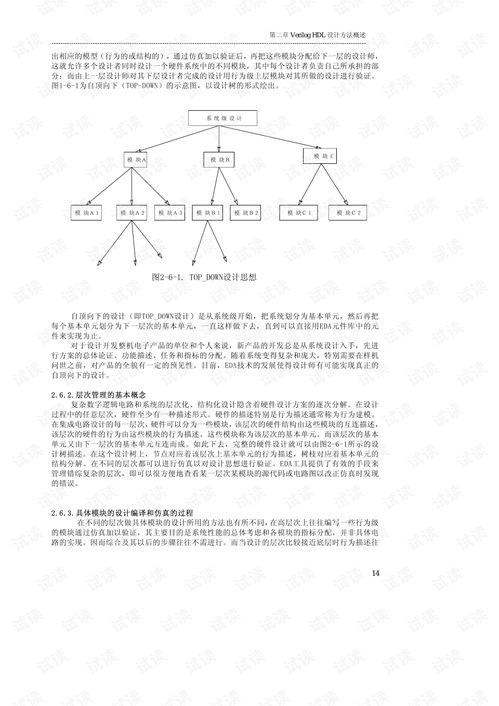

2. 系统级设计

根据需求分析,进行系统级设计,确定系统的模块划分、接口定义和功能描述。

3. 模块级设计

对系统中的每个模块进行详细设计,包括模块的内部结构、接口定义和功能描述。

4. 仿真验证

使用仿真工具对设计进行验证,确保系统满足设计要求。

5. 代码实现

将设计转换为System Verilog代码,并进行编译和综合。

6. 下载和测试

将生成的比特流文件下载到FPGA或ASIC芯片中,进行实际测试。

四、System Verilog在实际项目中的应用

System Verilog在数字系统设计中具有广泛的应用,以下列举几个典型应用场景:

1. 通信系统设计

System Verilog可以用于设计通信系统中的各个模块,如调制解调器、基带处理器、物理层等。

2. 存储器设计

System Verilog可以用于设计存储器控制器、存储器接口等模块,如DDR4控制器、NAND Flash控制器等。

3. 图形处理器设计

System Verilog可以用于设计图形处理器中的各个模块,如渲染器、着色器、纹理映射器等。

4. 网络处理器设计

System Verilog可以用于设计网络处理器中的各个模块,如MAC控制器、交换机、路由器等。

System Verilog作为一种强大的数字系统设计工具,在各个领域都得到了广泛应用。本文介绍了System Verilog的基本概念、设计流程以及在实际项目中的应用,希望对读者有所帮助。

教程资讯

教程资讯排行